This is a joint effort of Faculty of Electrical Engineering and Faculty of Information Technology to provide open tools and materials for teaching computer architecture principles.

- FEL: B35APO Computer Architectures

- FIT: BI-APS Architectures of Computer Systems

- FEL: B4M35PAP Advanced Computer Architectures

- WebEvaluator for QtRvSim (direct link to the web interface)

-

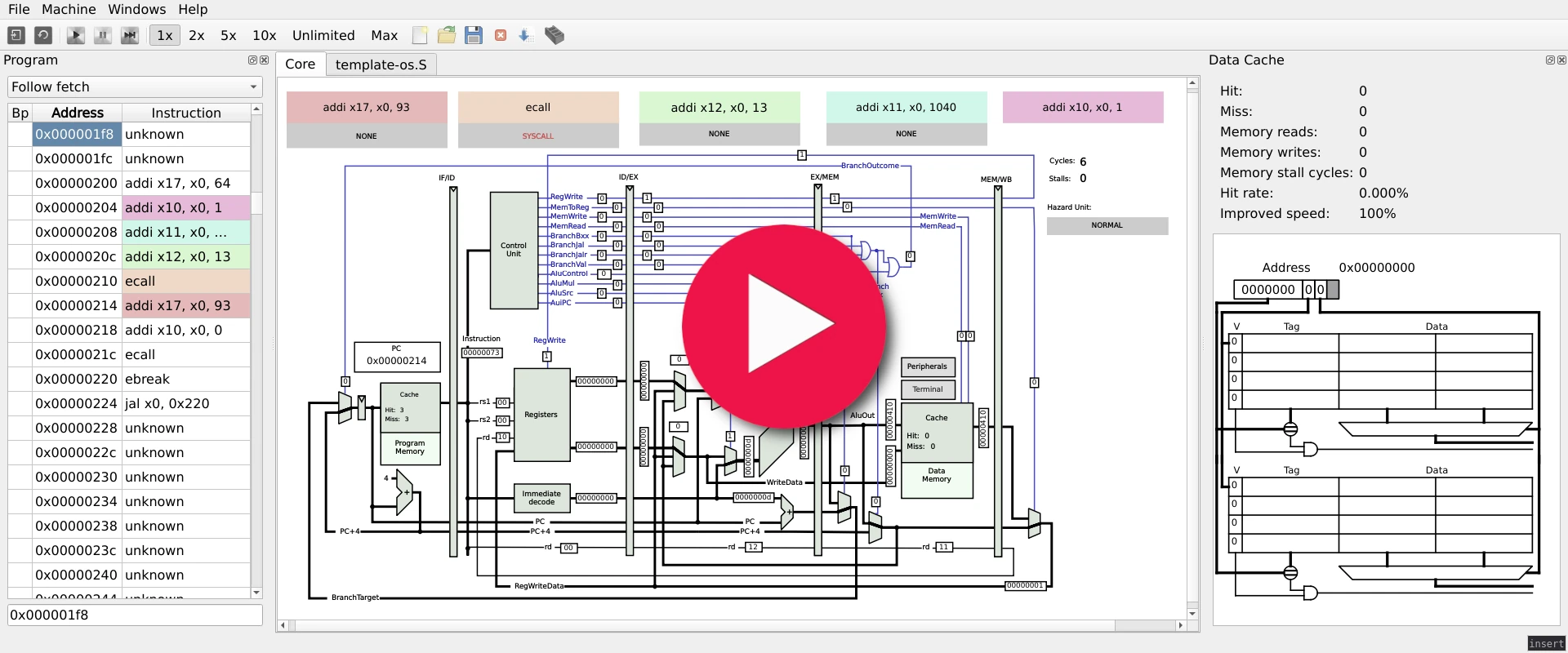

FOSDEM 2023 QtRVSim—Education from Assembly to Pipeline, Cache Performance, and C Level Programming in Brussels, Slides

-

QtRvSim – RISC-V Simulator for Computer Architectures Classes @ Embedded World Conference 2022

-

QtRvSim has been presented by Jakub Dupák at RedHat organized DevConf.cz mini in Brno, Video, Slides

-

RISC-V International Academic and Training SIG: QtRvSim - RISC-V Simulator with Cache and Pipeline Visualization (YouTube)

- Dupák, J.; Píša, P.; Štepanovský, M.; Kočí, K. QtRVSim – RISC-V Simulator for Computer Architectures Classes In: embedded world Conference 2022. Haar: WEKA FACHMEDIEN GmbH, 2022. p. 775-778. ISBN 978-3-645-50194-1.

Please reference above article, if you use QtRvSim in education or research related materials and publications.